Interconnects Built for AI Scale

Lightmatter’s photonic chips form a complete interconnect platform. Passage™ interconnects and Guide® light engines scale networking for AI supercomputers.

Photonic Interconnect

Passage

Complete photonics roadmap from NPO and OBO to 2D and 3D CPO and 3D Interposers. Edgeless I/O architecture enabling unlimited bandwidth scaling.

Explore Passage →VLSP Light Engine

Guide

Very Large Scale Photonics technology. The universal light source designed for the entire photonics industry.

Explore Guide →Platforms

Passage L200

Designed for frontier-scale training. Supports 32 to 64 Tbps of aggregate bandwidth through co-packaged optics, using 112G PAM4 signaling to enable dense and fast interconnects.

Passage L20

Accelerate your optics integration roadmap. Delivers 12.8 Tbps of aggregate bandwidth and 4x pluggable density, enabling high-capacity deployments in compact systems.

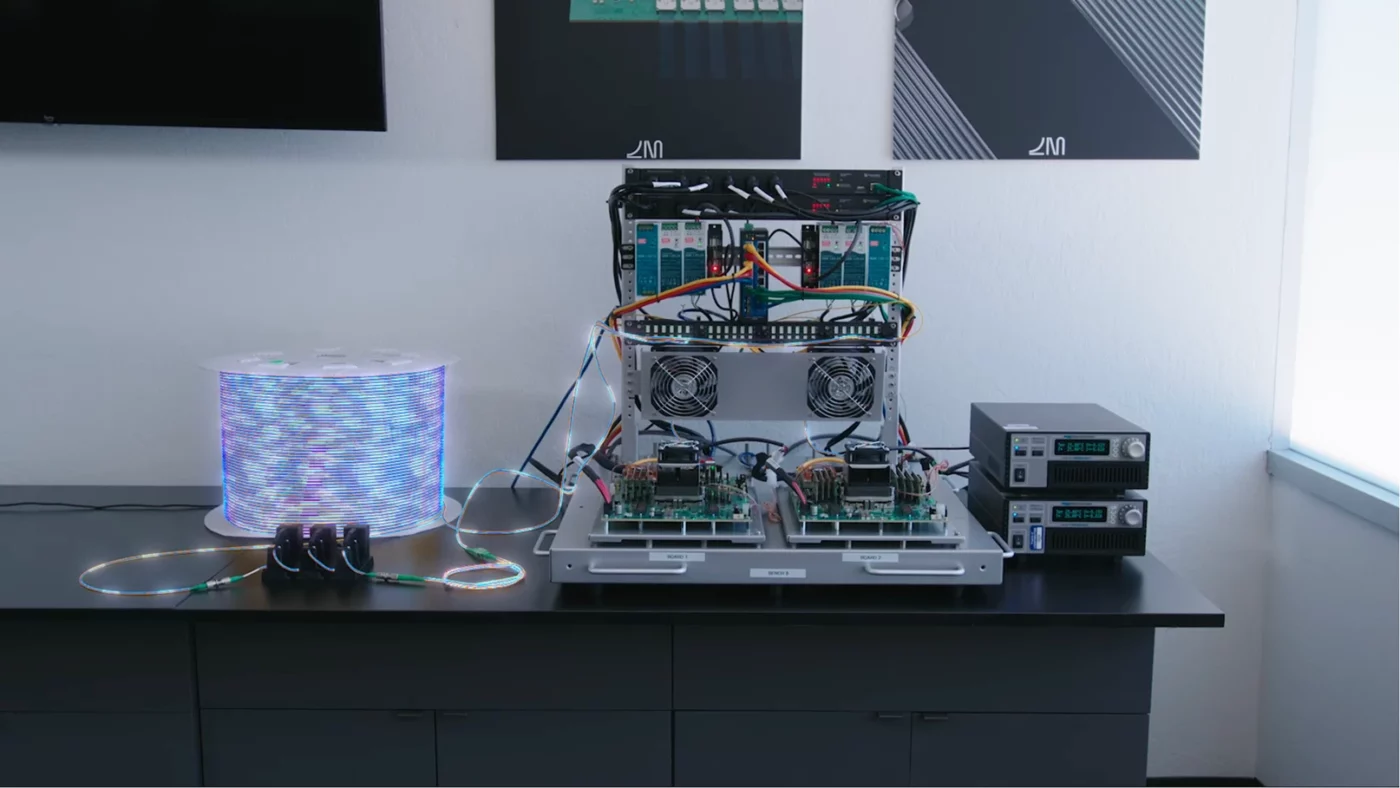

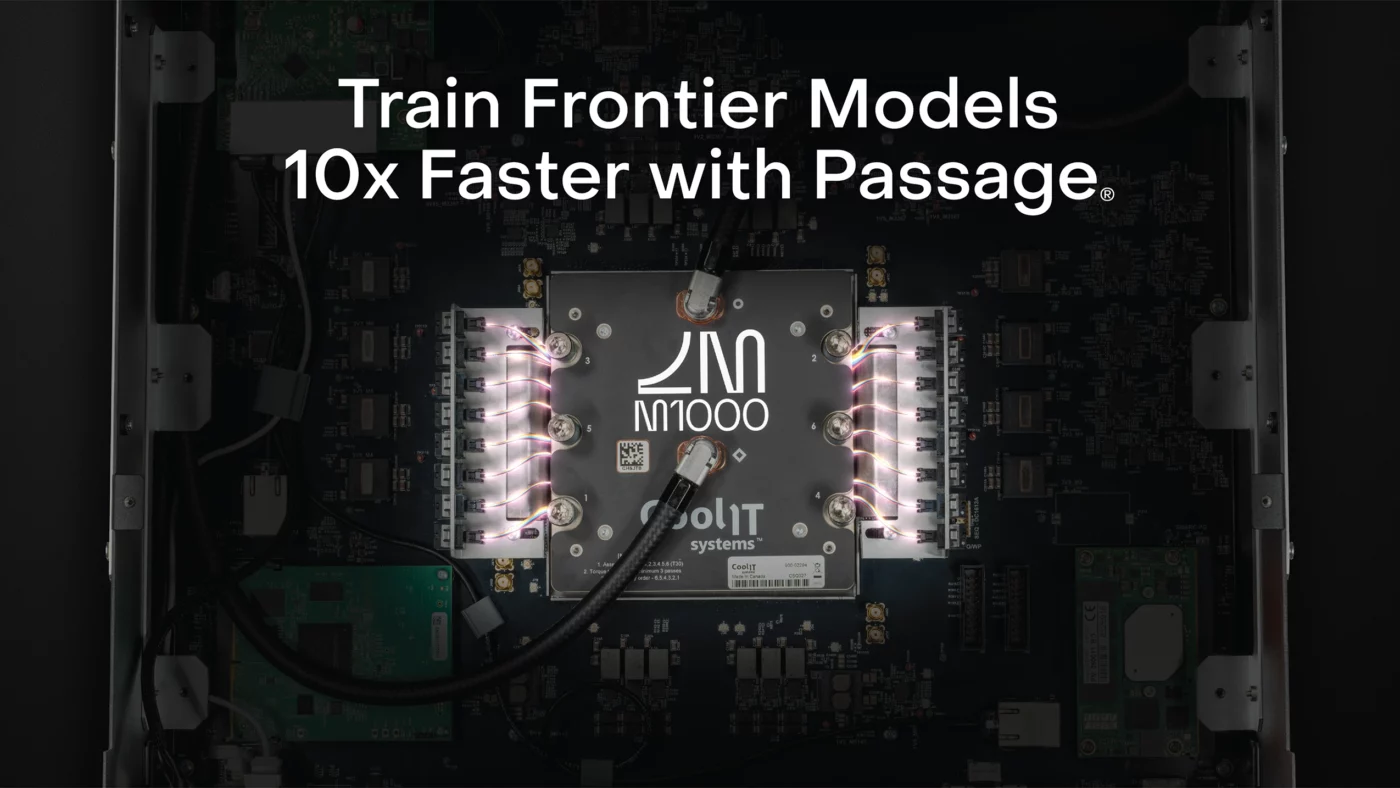

Passage M1000 EVK

A rack-level 3D photonic interposer reference platform delivering 114 Tbps across a 4,000 mm² footprint.

Passage EVK100

A high-bandwidth bidirectional link reference platform delivering up to 3.2 Tbps per fiber at 1.9 pJ/bit.

Passage EVK50

A 16-wavelength bidirectional link reference platform delivering 800 Gbps per fiber at 2.6 pJ/bit.

Guide 1 EVK

A 16-wavelength VLSP Light Engine powering 51.2 Tbps at 800 Gbps per fiber at ±20 GHz wavelength accuracy.

Lightmatter’s 8X Leap: World-First 16-Wavelength Bidirectional Optical Link for AI Data Centers

World-first 16-wavelength bidirectional optical DWDM Link on a strand of standard single mode fiber. This Lightmatter breakthrough represents an 8X leap in bidirectional fiber bandwidth density and a doubling of radix, paving the way for the next generation of AI data centers.

Passage M1000: Powering the Next 1000x in AI Performance

Explore the Passage M1000 Reference System, a groundbreaking platform built around the Passage M1000 3D Photonic Superchip. Discover how this revolutionary photonic interconnect technology is changing the game for Artificial Intelligence (AI) infrastructure by enabling massive scale-up bandwidth and radix,

Featured Publication

Accelerating Frontier MoE Training with 3D Integrated Optics

New research published by Lightmatter demonstrates how 3D CPO enables unprecedented AI training scale.

arXiv:2510.15893 • October 2024

8x scale-up capability for frontier AI training

- 8x larger scale-up domain: 100,000+ GPUs in single coherent fabric

- 2.7x reduction in time-to-train for trillion-parameter MoE models

- First demonstration of multi-rack photonic scale-up for frontier AI

“3D CPO (Passage) enabled GPUs and switches result in a 2.7x reduction in time-to-train, unlocking unprecedented model scaling.”

AI scaling is constrained by electrical interconnect

Electrical I/O has reached its limits

Training frontier AI models requires moving petabytes of data between GPUs. Current electrical SerDes technology is fundamentally bandwidth and reach limited—chips are running out of edge space for I/O and scale-up domains are confined to a single rack.

The result: Powerful GPU clusters sit idle waiting for data.

Infrastructure can’t keep up

Model parameters have grown 240x in 3 years. Cluster sizes have grown 10x. But interconnect bandwidth has only improved 2x.

The gap is widening: Without a breakthrough in interconnect technology, next-generation AI training becomes economically infeasible.

Passage is built by Lightmatter to solve the hardest problems in AI

01

Frontier Training

100,000+ GPU clusters for trillion-parameter models

02

Multi-Modal AI

Video, image, and audio foundation model training

03

Reasoning Models

Scalable tensor parallelism for inference

04

Inference at Scale

Serving foundation models to billions of users

Production Ready at Scale

Valuation (Oct 2024)

$4.4B

Total Funding

$850M

Headquarters

Mountain View, CA

Manufacturing Partners

Standards Bodies

Ready to eliminate your AI infrastructure bottlenecks?

Connect with our team to see how Lightmatter can transform your AI networking and compute architecture.