## 2IGHTMATTER

# Photonic-Enabled Heterogeneous Integration: The Future of AI System Scaling

Sandeep Sane, Ph.D.

Senior Director, Head of Packaging Technologies

#### \$850M RAISED

Fidelity Google Ventures Sequoia Spark Capital Viking

T. Rowe Price Matrix Partners SIP Capital MIT Stanford

## OFFICES

Mountain View (HQ)

**Boston**

## EMPLOYEΣS

Founder, CEO

Sujatha Wagle VP, Supply Chain Ops

Praveen Kukkamalla VP, Sales

Darius Bunandar, PhD Founder, Chief Scientist

Ritesh Jain SVP, Engineering & Ops

Beth Keil SVP, People

General Counsel

VP, Cloud Services Sales

Thomas Graham Founder

**Bob Turner** SVP. Sales & Solution Arch

Steve Klinger VP. Product

VP, Photonics & Si Eng

Head of Creative Marketing

## 311 PAZENTS

Granted & Pending

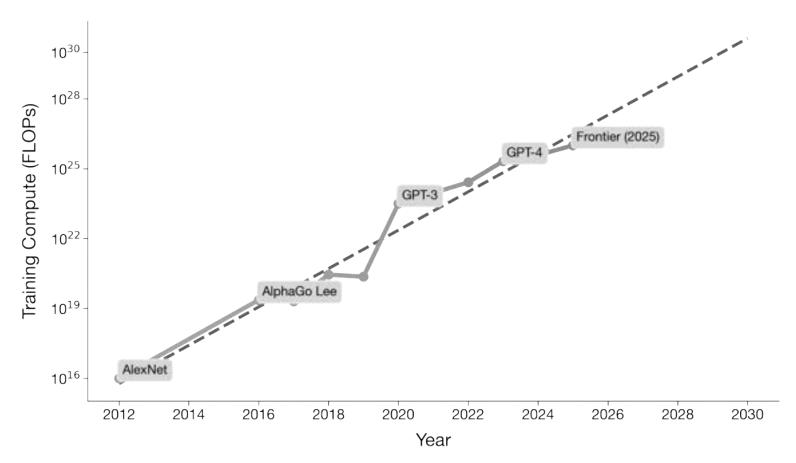

## 10<sup>9</sup> Growth in a Decade

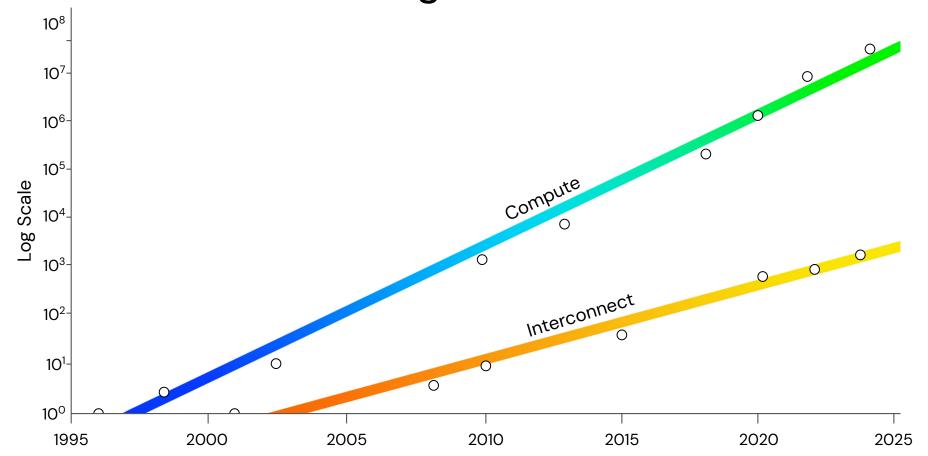

## Interconnect Progress Is Too Slow

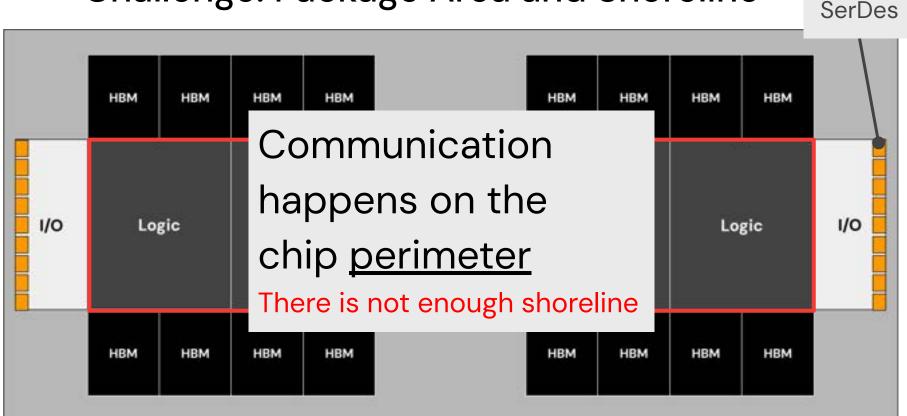

## Challenge: Package Area and Shoreline

A new paradigm is needed

ZIGHTMATTER

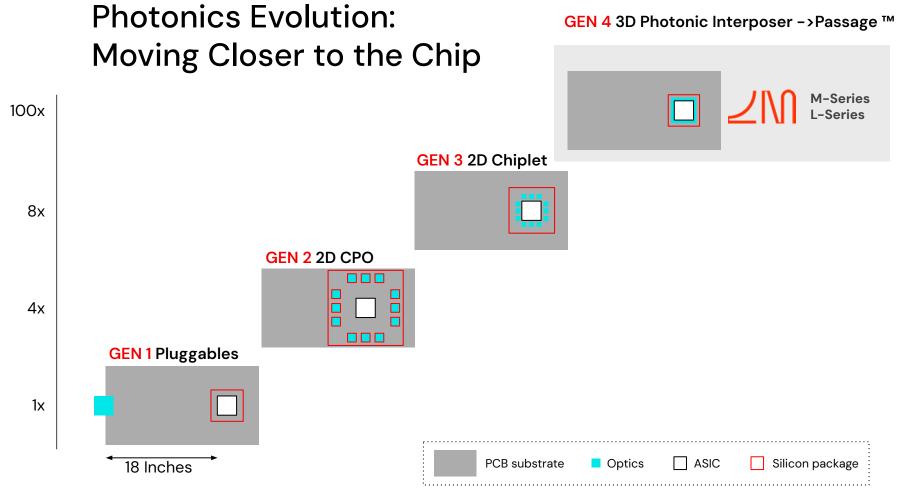

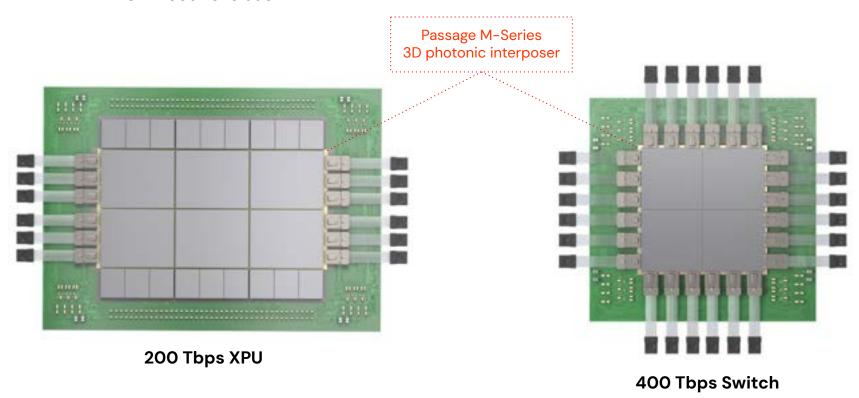

## Passage ™: 3D Photonic Interposer

#### **Photonic Integrated Circuit**

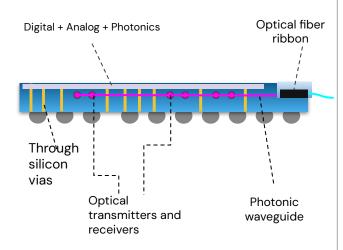

Passage Cross Section

(note: digital/analog can be integrated in top die; FAB choice dependent)

Passage value (3D integration) and density

optical waveguides stitched across reticle

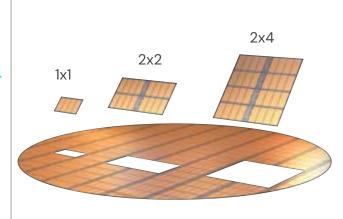

Passage scalability from single to multi-reticle

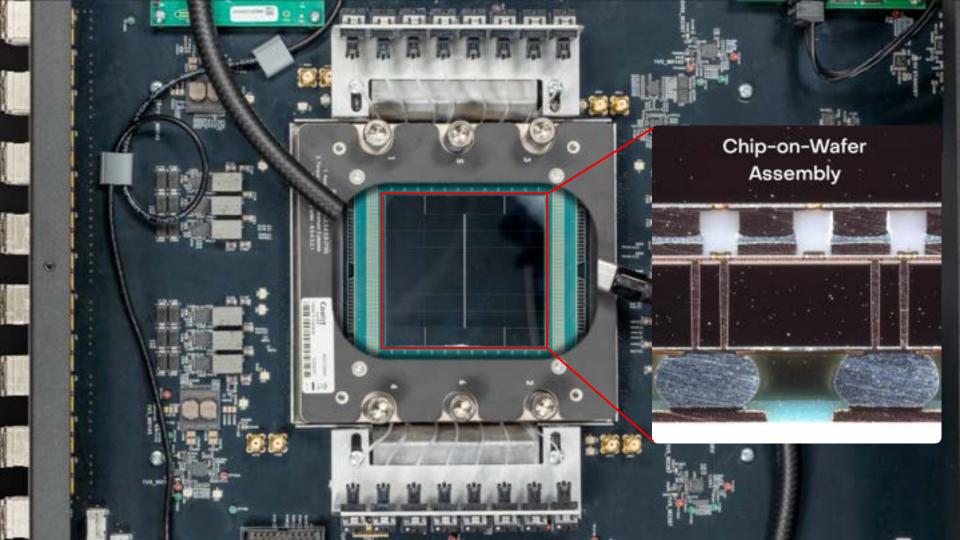

Built on 3D packaging technology and a Chip-on-Wafer assembly flow

**ZIGHTMATTER**

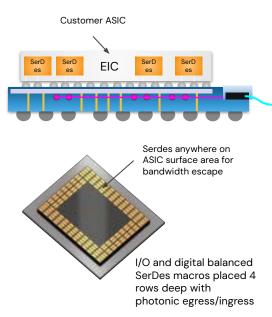

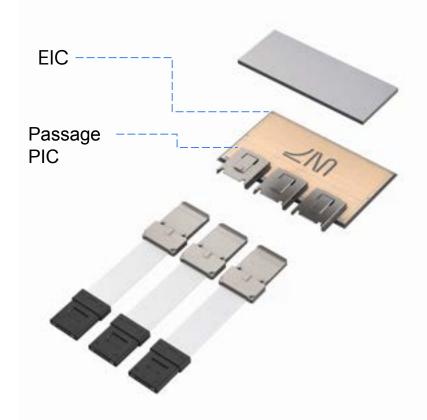

#### 3D CPO Requires Compact Optical Modulators and Receivers

Standard Package Example

Fiber array unit & **EIC** Pluggable connector **Cross Section** IO Chip **UCle** Optical fiber ribbon XPU/Switch Chip UCle Photonic Integrated Circuit **Package Substrate** Power & Signals Photonic waveguide Optical transmitters Through silicon vias and receivers

#### Standard processes today

- Bump pitch: ~120 μm

- Bump size: ~80 μm

- Area for a transmitter/receiver: 0.015 mm²

### Passage M-Series

Photonic Interposer

Available Now

## Passage™ L-series 3D CPO

- Single reticle

- I/O EIC with UCle & SerDes

- >1.5 Tbps/mm bandwidth density

- Detachable FAU

## 20 pluggables in the area of a quarter.

1.6 Tbps pluggables

**L-Series**

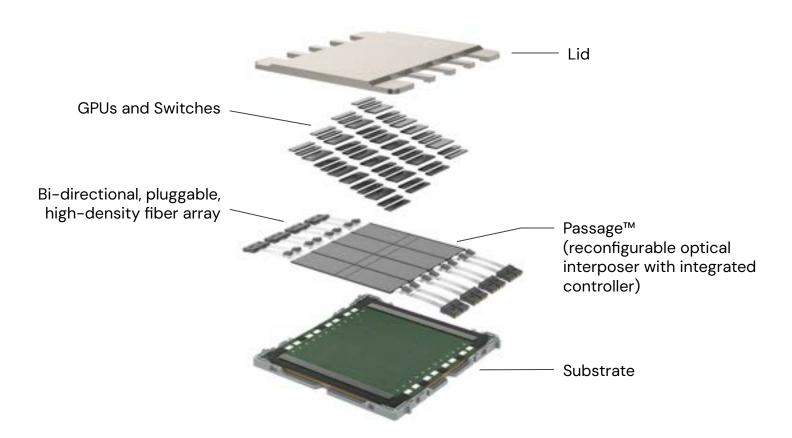

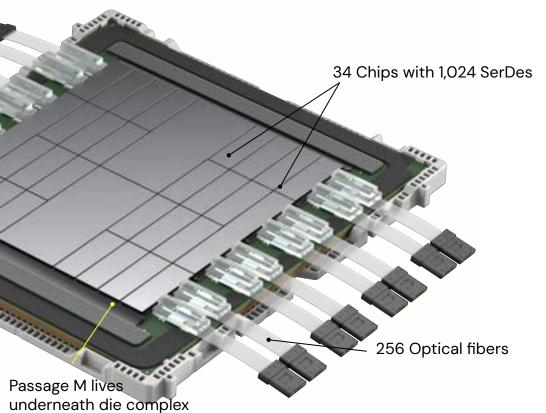

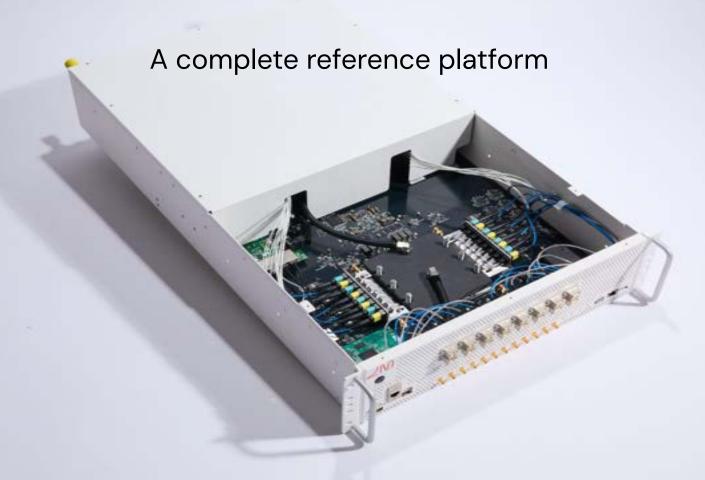

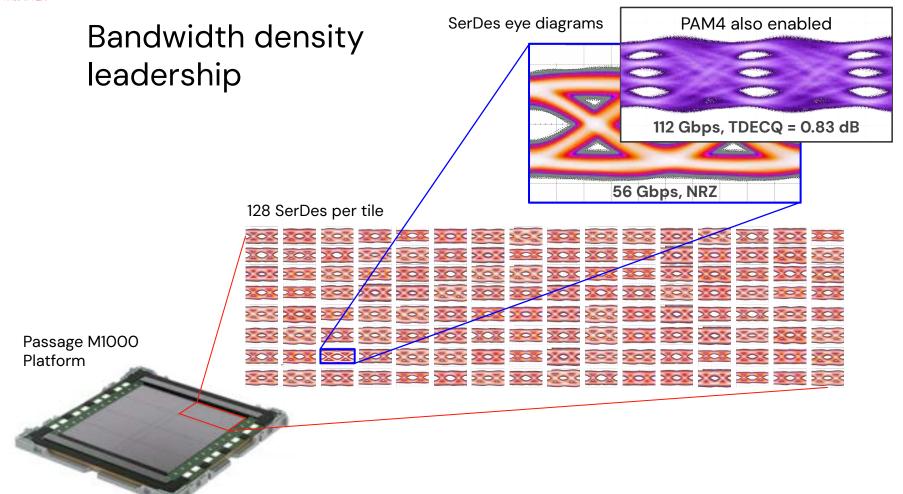

## Passage™ M Series: Multi-Reticle PIC

## Passage™ M Series

Photonic interposer reference platform

| Specifications           |                           |  |

|--------------------------|---------------------------|--|

| Bandwidth (Tx + Rx)      | Up to 114 Tbps            |  |

| # of SerDes              | 1024                      |  |

| Silicon die Complex      | 4,000 mm <sup>2</sup>     |  |

| Power delivery           | >1.4 W/mm² density        |  |

| Fibers                   | 256                       |  |

| Redundancy               | Optical circuit switching |  |

| Substrate Form<br>Factor | 91x85mm                   |  |

**Enables 114 Tbps total bandwidth.**

**ZIGHTMATTER**

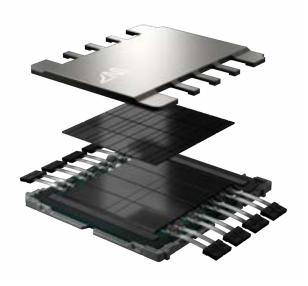

#### M1000 How it's built.

ASIC

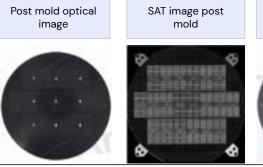

Post mold grind

PIC PIC

Wafer Test

TSV Reveal

RDL and bumping

CoW reflow: PIC wafer (TSV) to ASIC attach

Wafer level underfill, mold and grind

Wafer dicing

exposed optical

ASIC

System

Fiber attach with real time optical test

Package e-test (Known good PKG)

Post substrate attach reflow

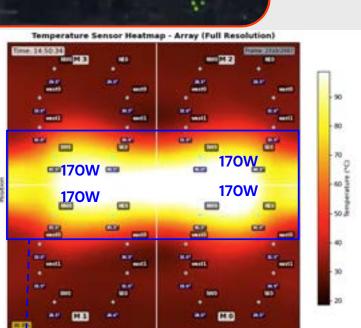

Power delivery and / thermal load

FLOW 1.8LPM LIQ TEMP 24.5C

369mm<sup>2</sup> thermal test chip, power density 1.47W/mm<sup>2</sup>. Passage TSVs support >2.5A/mm<sup>2</sup>.

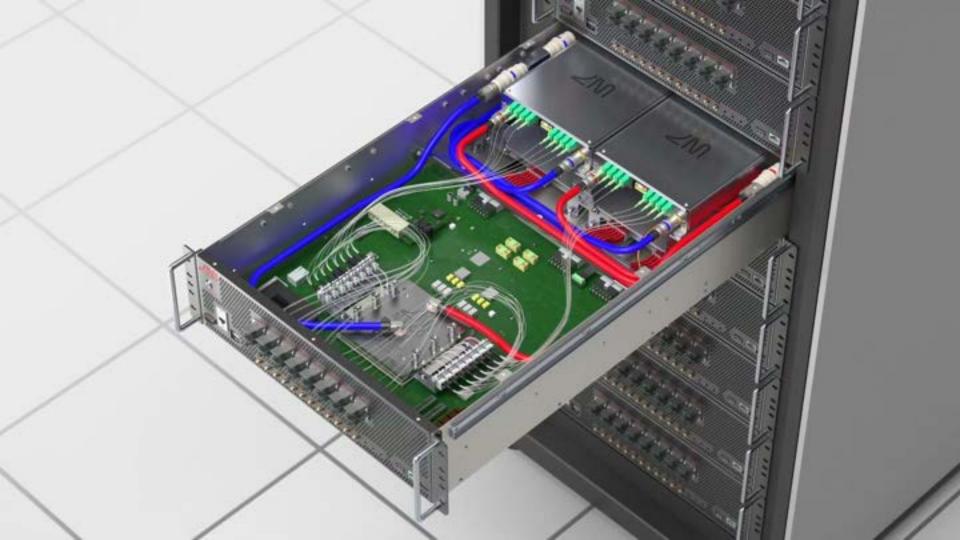

## 3D Interposer scale-up and out to 1M nodes

The M1000 revolution

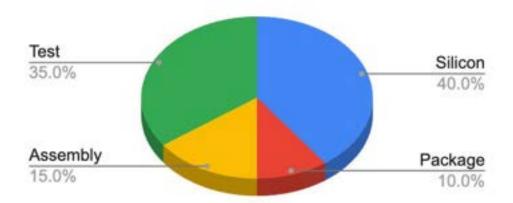

### SPAT Costs and the Need for continued Innovation

Silicon, Package, Assembly, Test

Note: Graph shown for demonstration purposes only

For SiPho Relative Packaging, Assembly and Test (PAT) cost % is increasing

PAT cost challenges in SiPho:

- In assembly: fiber attach yields

- 2. In test: test times are much higher

DFM/DFT-driven product architecture is must for high volume SiPho manufacturing and cost reduction

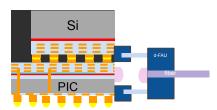

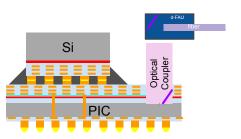

#### Fiber Attach Methods

Traditional FAU

Wafer Level Optical coupler

| V-Groove based Fiber Attach Methods            | Lens based: Detachable fiber attach            | LM Focus: Detachable fiber attach        |

|------------------------------------------------|------------------------------------------------|------------------------------------------|

| Package level assembly (interface on die edge) | Package level assembly (interface on die edge) | Wafer level assembly and test compatible |

| Not compatible with 3D Arch                    | Compatible with 3D Package Arch                | Compatible with 3D Package Arch          |

| XPU to OE D2D: Standard Package                | XPU to OE D2D: Standard & Adv. Package         | XPU to OE D2D: Standard & Adv. Package   |

| Passive or Active alignment                    | Active alignment                               | Passive or Active alignment              |

| Test with FAU after package assembly           | Test with FAU after package assembly           | Test with FAU at wafer level             |

| FAB: GF only                                   | FAB: GF & TSMC                                 | FAB: GF & TSMC                           |

| Serviceability: No                             | Serviceability: Yes                            | Serviceability: Yes                      |

| Limited scalability to HVM (\$\$\$)            | Scalability to HVM (\$\$)                      | HVM scalable solution (\$)               |

LM driving strong ecosystem partnership to bring detachable FAUs to HVM scale

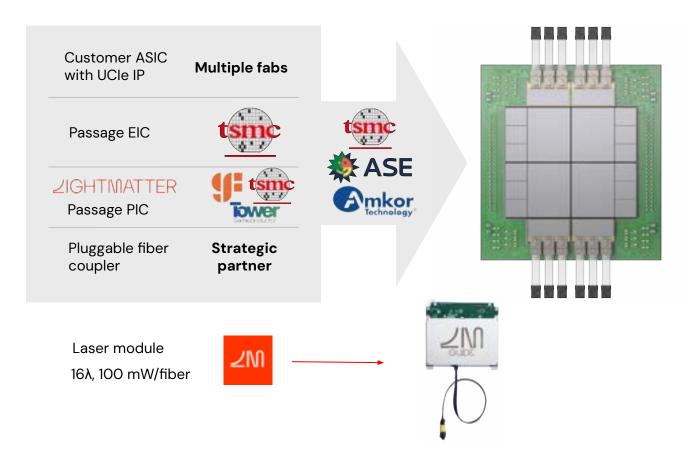

## Optimized end-to-end and production-ready